Why it matters: Samsung has rolled out its inaugural mobile system-on-chip built using cutting-edge 3nm process technology featuring gate-all-around transistors. But that's not even the most impressive part - this silicon was designed with artificial intelligence-powered EDA tools from Synopsys.

The two companies announced the feat this week, shedding light on how Samsung leveraged Synopsys' AI-driven software suite to streamline the entire SoC design process. From architectural planning to physical implementation and verification, machine learning algorithms handled those painstaking tasks usually assigned to human engineers.

Synopsys' toolkit, branded as Synopsys.ai, comprises three core AI wizards - DSO.ai for chip design, VSO.ai for functional verification, and TSO.ai for silicon testing. By crunching massive datasets with deep learning models, these AI modules automated and accelerated notoriously time-consuming chip development stages.

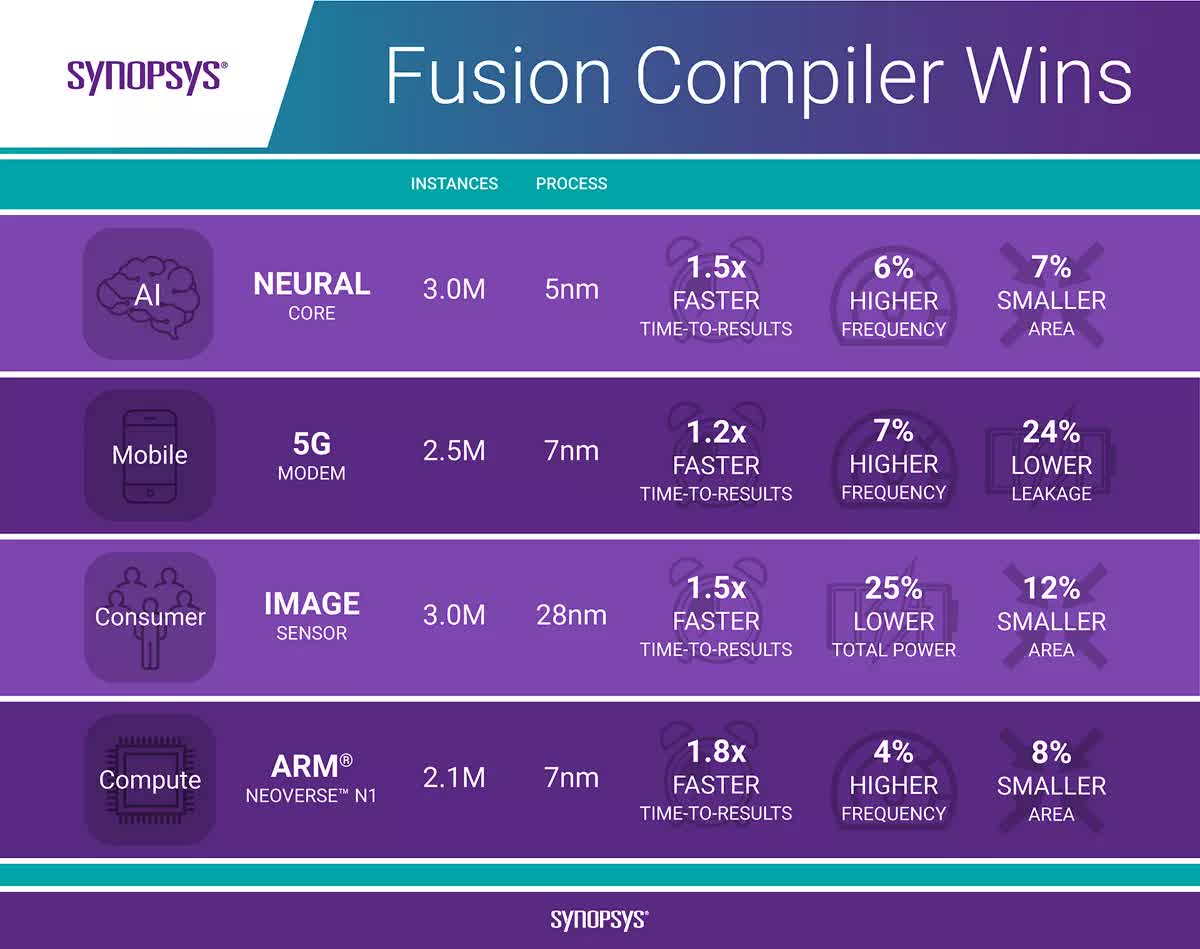

For Samsung's mystery mobile processor, AI took the reins on everything from place-and-route layout to signoff and optimization across performance, power, and area metrics. Synopsys claims its Fusion Compiler software alone saved Samsung's team weeks of arduous manual labor.

The results are noteworthy. Thanks to AI-optimized techniques such as design partitioning, multi-source clocking, and wire mapping, Samsung's 3nm SoC boasts a 300MHz boost in peak CPU frequencies along with a 10 percent reduction in dynamic power consumption. That's not too shabby for a silicon brain designed by, well, artificial brains.

This marks the company's first complex design iteration on its latest 3nm GAAFET (gate-all-around FET) manufacturing technology. Despite introducing the industry's first commercial GAAFET node almost two years ago, Samsung had thus far limited it to relatively simple cryptocurrency mining processors.

With this Synopsys-assisted SoC, Samsung finally enters the realm of high-performance GAAFET silicon for premium mobile devices. The AI design flow could aid the chipmaker in accelerating GAAFET yields for future Exynos processors in flagship Galaxy smartphones and tablets.

"The relentless demand for ever-better PPA and energy efficiency in high-performance mobile chips is driving the need for high-performance core-specific EDA optimization across the full stack," said Shankar Krishnamoorthy, general manager of the EDA Group at Synopsys.

"Our extensive set of PPA-boosting capabilities targeted for CPUs and GPUs across the Synopsys AI-driven EDA suite and IP portfolio enables our mutual customers to successfully design chips with the highest quality-of-results for the most advanced Samsung GAA processes."

Neither company is divulging details on the specific 3nm technology this AI-architected mobile chip utilizes. However, speculation suggests it likely employs Samsung's more refined, second-gen SF3 node rather than the earlier SF3E process.